Cortex®-A9 processors and a MicroBlaze processor, each running its own bare-metal software application, and allowing each processor to communicate with the other through shared memory.

CA9랑 MB 프로세서 두개에 bare-metal sw app 각 각 올리고 커뮤니케이션으로 shared memory를 쓴다.

Zynq-7000 AP SoC는 PL (Programmable Logic)에 상주하는 MicroBlaze 프로세서에서도 액세스 할 수있는 공통 메모리 및 주변 장치를 공유하는 2 개의 Cortex-A9 프로세서를 제공합니다. (CA9는 둘 중 하나만 사용함)

AMP (Asymmetric Multiprocessing)는 여러 프로세서가 공유 리소스를 통해 해당 응용 프로그램을 느슨하게 연결할 수있는 자체 운영 체제 또는 베어 메탈 응용 프로그램을 실행할 수 있도록하는 메커니즘입니다.

In this AMP example, the bare-metal application running on CPU0 is the master of the system and is responsible for:

• System initialization • Releasing PL reset • Communicating with MB0 • Sharing the UART with MB0

The bare-metal application running on MB0 is responsible for:

• Communicating with CPU0 • Servicing interrupts from a core in the PL • Sharing the UART with CPU0

Zynq SoC PS에는 CPU0 전용 개인 리소스와 MB0에서 액세스 할 수있는 기타 리소스가 포함되어 있습니다. AMP 구성에서 디자인을 실행할 때 두 CPU가 이러한 공유 리소스에 대해 경합하지 않도록주의해야합니다.

Examples of some of the private resources are:

• L1 cache • Private peripheral interrupts (PPI) • Memory management unit (MMU) • Private timers

Examples of some of the shared resources are:

• Interrupt control distributor (ICD) • DDR memory • OCM • Global timer • Snoop control unit (SCU) and L2 cache • UART0

이 예에서 CPU0은 마스터로 취급되며 공유 자원을 제어합니다. MB0이 공유 자원의 제어를 요구해야하는 경우, 요청을 CPU0에 전달하고 CPU0이 자원을 제어하게해야합니다. 이 참조 디자인의 복잡성을 최소한으로 유지하기 위해 MB0에서 실행되는 베어 메탈 응용 프로그램은 공유 리소스에 대한 액세스를 제한합니다.

OCM은 두 프로세서가 서로 통신하는 데 사용됩니다. DDR 메모리와 비교할 때 OCM은 두 프로세서 모두에서 매우 높은 성능과 낮은 대기 시간 액세스를 제공합니다. 두 프로세서 모두에서 OCM에 대한 캐시 액세스를 비활성화하면 결정적 액세스가 더욱 보장됩니다.

공유 리소스 관련 문제를 방지하기 위해이 디자인에서 취한 조치는 다음과 같습니다.

• DDR memory: CPU0 has only been made aware of memory at 0x00100000 to 0x2FFFFFFF. MB0 uses DDR memory from 0x30000000 to 0x3FFFFFFF for its bare-metal application.

• OCM: Accesses to OCM are handled very carefully by each CPU to prevent contention. A single OCM address location is used as a flag to communicate between the two processors. CPU0 initializes the flag to 0 before starting MB0. When the flag is zero, CPU0 owns the UART. When the flag is not zero, MB0 owns the UART. Only CPU0 sets the flag and only MB0 clears it.

MicroBlaze Address Map

0x30000000–0x3FFFFFFF : PS DDR via MB0 cache accesses through the HP ports. Refer to Zynq-7000 All Programmable SoC Technical Reference Manual [Ref 1] for more details regarding access to the PS DDR from the HP ports.

Software : FSBL, Bare-metal app for CPU0/MB0

Inter-Processor Communication

예제 디자인에서 프로세서 간 통신은 세마포어 플래그입니다. 세마포어가 설정되면 MB0이 UART를 소유하고 MB0에 의해 지워지면 CPU0은 UART를 자유롭게 사용할 수 있습니다. 이것은 리소스를 공유하는 간단한 메커니즘입니다. 지연 시간이 짧은 공유 리소스이므로 OCM 메모리가 선택됩니다. 또한이 OCM 영역은 캐시되지 않으므로 메모리 액세스가 일관되고 결정적입니다.

| 용어 | 풀이 |

| PL | programmable logic |

| HP | high-performance |

| PS | processing system |

| OCM | on-chip memory |

| VIO | virtual input/output |

| ILA | integrated logic analyzer |

| S_GP0 | slave general-purpose port |

| MB0 | MicroBlaze processor |

| FSBL | First stage boot loader |

'개발' 카테고리의 다른 글

| tvm (0) | 2019.12.21 |

|---|---|

| stack (0) | 2019.12.17 |

| 어셈블리어 (0) | 2019.12.17 |

| AArch64 generic timer (0) | 2019.12.09 |

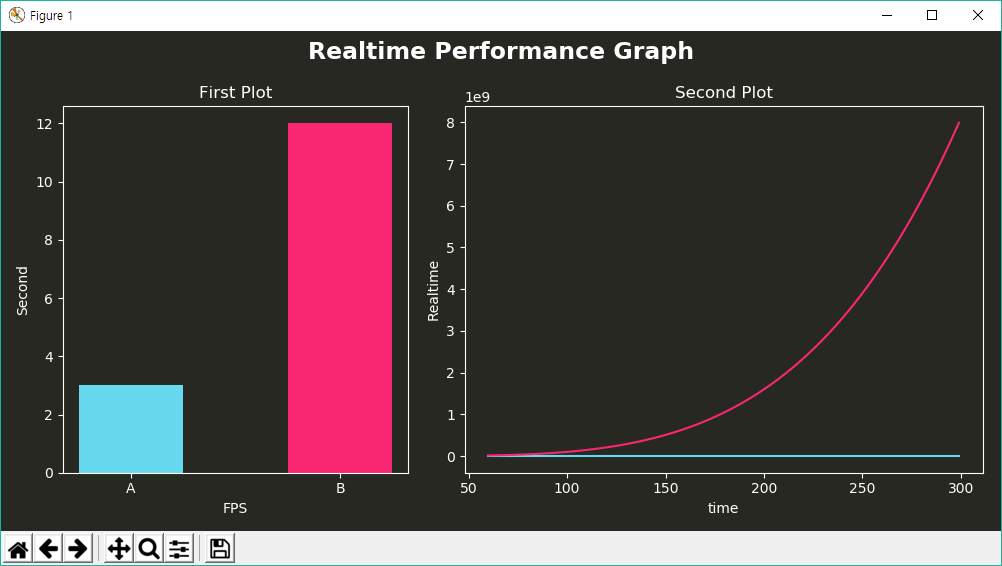

| plot graph color (0) | 2019.10.04 |